## NR Code No: A0602, A5502, A5702 JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD M.Tech I Semester Examinations, March/April 2011 VLSI TECHNOLOGY AND DESIGN (COMMON TO DIGITAL SYSTEM AND COMPUTER ELECTRONICS, EMBEDDED SYSTEMS, VLSI SYSTEM DESIGN) **Time: 3hours**

Max. Marks: 60

## Answer any five questions All questions carry equal marks

- Explain the process of fabrication for CMOS technology with neat diagrams 1.a)

- Compare B<sub>i</sub>CMOS technology with other Technologies. b)

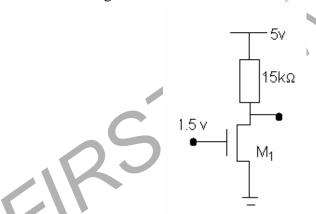

- Calculate I<sub>D</sub> and V<sub>DS</sub> if  $k_n = 100 \ \mu A/v^2$ ,  $V_{tn} = 0.6v$  and W/L =3 for transistor M, in the 2.a) circuit in shown in figure.

- b) Determine the pull up to pull down ratio for an nMOS inverter driven by another inverter. [6+6]

- 3.a) Write the design rules for contact cuts.

- What are the limitations for scaling? b)

- What are the various construction rules for transistors? c)

- What are the advantages of pseudo nMOS logic? Draw the circuit diagram of pseudo -4.a) nMOS NOR fate and explain its operation.

- Draw the model for derivation of delay unit and derive its value for 5 µm technology. b)

[6+6]

[12]

[6+6]

- 5.a) What is barrel shifter? How to use it in VLSI design?

- b) How to list a combinational logic networks? Give some simulation tools. [6+6]

Contd.....2

## www.firstranker.com

## ::2::

| <ul><li>6.a) Draw a circuit diagram for 4 – transistor SRAM cell and explain how it stores data?</li><li>b) Write short notes on the clocking discipline for sequential systems.</li></ul>               | [6+6] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <ul><li>7.a) What is mean by floor planning? Explain the different methods of floor planning.</li><li>b) Design a circuit for input pad connectivity and explain its necessity in chip design.</li></ul> | [6+6] |

| <ul><li>8.a) Explain the various Architectures to reduce the power.</li><li>b) Explain how scheduling determines time cost.</li></ul>                                                                    | [6+6] |